4. GMSL2-10GbE 変換モジュール ハードウェア リファレンス マニュアル#

4.1. 概要#

GMSL2-10GbE変換モジュールは、最大8つのギガビット・マルチメディア・シリアル・リンクTM (GMSL) インターフェースからホストシステムへの10Gbイーサネットリンクを介した低遅延データ転送を可能にするエッジコンピュートプラットフォームです。

このシステムには、GMSL2/1からCSI-2への変換を行う2つのMAX96724クワッドトンネリング・デシリアライザを実装し、最大8つのGMSLカメラの接続が可能です。カメラからのビデオデータは、MAX96724 MIPI-CSI2インターフェースを介してAMD KV26システムオンモジュールに送り込まれ、そこでビデオデータを10Gbイーサネットリンクに集約して中央処理ユニットに送信するためのロジックが実装されています。

ハードウェア タイムスタンプ機能を備えた IEEE1588 高精度時間プロトコル (PTP) がサポートされており、ホスト システムやその他のエッジ デバイスとの正確な同期が可能になります。AD9545 デュアル DPLL/IEEE1588、1pps シンクロナイザおよびジッタ クリーナーは、10Gb イーサネット インターフェイスと PTP ロジックに必要なクロックを生成するために使用されます。

16 個の汎用 I/O ピンはソフトウェアで設定可能な機能を備え、3.3V の電圧レベルで動作します。

RS232 専用インターフェースを使用して、GNSS デバイスなどの UART 周辺機器を接続できます。

4.2. 物理仕様#

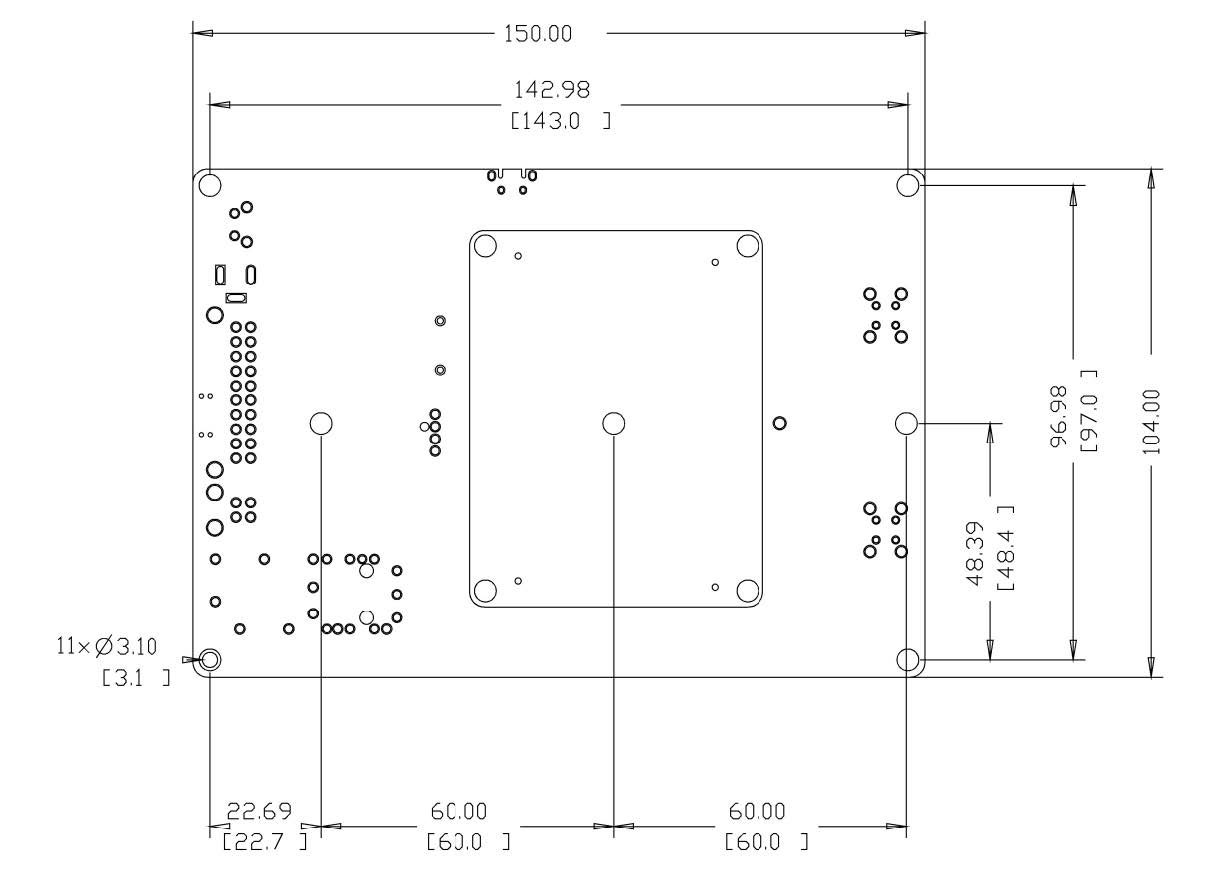

図 4.14 外形図#

4.3. 電力・熱仕様#

パラメータ |

最小 |

標準 |

最大 |

単位 |

コメント |

供給電圧 |

10 |

12 |

48 |

V |

主電源コネクタとI/Oコネクタの組み合わせ。バレルジャック電源コネクタ1個、主電源または補助電源に使用可能 |

出力定格 |

5 |

24 |

W |

システム処理負荷に依存 |

|

動作温度 |

-40 |

60 |

degC |

キャリアPCBレベルで測定。動作温度範囲を確保するには適切な冷却を実施する必要があります。 |

4.4. 入力/出力インターフェース#

4.4.1. SFP+ 光 10Gb イーサネット#

FPGA の 10Gb イーサネット MAC と PHY

ハードウェアタイムスタンプ付きIEEE 1588

SFP+ケージ P/N: 2007194-1

SFP+コネクタP/N: 1888247-1

4.4.2. RS232 シリアル#

電流制限・過電圧保護対応 3.3V

機能:

カメラトリガー/フラッシュ信号 x8

PPS出力x1

PPS入力x1

PWM出力x1

I2C コネクタ P/N: 430452023

4.4.3. GPIO#

16ポート 電流制限・過電圧保護対応 3.3V

カメラトリガー/フラッシュ信号 x8

PPS出力x1

PPS入力x1

PWM出力x1

I2C

コネクタ P/N: 430452023

4.4.4. GMSL#

2 x HFM クアッドタイプ ミニ Fakra コネクタ

コネクタ P/N: 2304168-9

4.4.5. SDカード#

マイクロSDカードホルダー、押して取り出す

4.4.6. USB2.0#

Linux OS のコンソール インターフェース

4.4.7. JTAG#

Kria SoC PL デバッグ インターフェース

4.5. 信号処理#

4.5.1. AMD Kria K26 SoM#

産業グレードの SoM (P/N: SM-K26-XCL2GI)。冷却機構は含まれていません

4.6. ファームウェアとソフトウェア#

4.6.1. ファームウェア#

デスクトップ UI 無しのカスタム Linux イメージ

イーサネット経由の Linux イメージ更新

LinuxイメージはXilinx Kria SoM eMMCまたはSDカードに保存

4.6.2. システム構成とステータスのHTMLユーザーインターフェース#

設定可能なIPアドレスとポート経由でアクセス可能

システム構成とステータスのリモート制御

RTPコントロール

カメラトリガー設定

ストリーミング設定

PTP設定

カメラ設定

4.6.3. SSH経由のリモートシステム構成とステータス#

イーサネットインターフェース経由でシステムへのSSHアクセス

Linux標準ドライバインターフェースとツールを介してシステムのすべての機能にアクセス可能

4.7. 同期#

4.7.1. IEEE1588#

ハードウェアタイムスタンプ

スレーブまたはマスターとして設定可能

4.8. カメラ制御とデータ形式#

4.8.1. カメラトリガーコントロール#

各カメラは内部で独立してトリガー可能

デシリアライザーの FSYNC + GPIO を使用して、1 つのデシリアライザーで 4 台のカメラすべてを独立してトリガー可能

システム ToS に関連する内部トリガー

各内部トリガーは周波数、位相、デューティサイクルを設定可能: 1Hz~200Hz

出力として設定された外部GPIOは、内部カメラトリガーと同じ方法で制御可能

入力として設定された外部GPIOは、個々のカメラを直接トリガー可能

サブミリ秒レベルのトリガージッター

トリガー遅延も設定可能(位相設定+遅延により、さまざまなカメラトリガーと露出特性を補正)

4.8.2. データのタイムスタンプ#

ビデオ パケットには PTP 同期システム時刻のタイムスタンプが付けられます。タイムスタンプ形式のオプション:

32ビットNTP

96ビットPTP

画像のタイムスタンプは、FPGA タイムスタンプ (PTP 同期システム時間) を使用して、トリガー (FSYNC)、フレームの終了、またはフレームの開始時に生成可能

タイムスタンプのオフセットを設定可能

4.8.3. ビデオデータ形式#

UDPデータ出力

RFC3550およびRFC4175に準拠したRTP